# TEXAS INSTRUMENTS

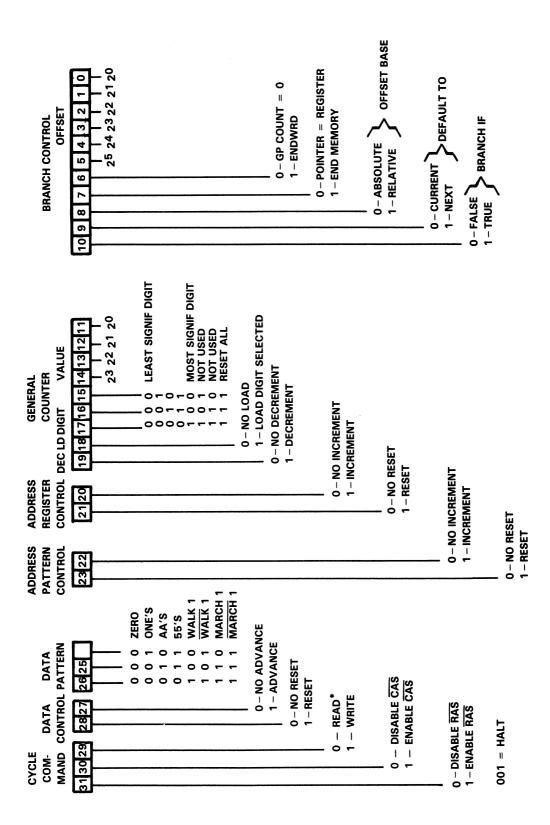

# TMS4164 64K Dynamic RAM Reliability Report

# NOTICE

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible. Information contained in this publication is believed to be accurate and reliable. However, responsibility is assumed neither for its use nor for any infringement of patents or rights of others that may result from its use. No license is granted by implication or otherwise under any patent or patent right of Texas Instruments or others.

Copyright © 1982

Texas Instruments Incorporated

Second Printing

# TMS4164 64K Dynamic RAM Reliability Report

# **TABLE OF CONTENTS**

| Section                                            | Page |

|----------------------------------------------------|------|

| INTRODUCTION                                       |      |

| Background                                         |      |

| Definitions                                        |      |

| MEMORY DESIGN                                      |      |

| Background                                         |      |

| The Cell                                           |      |

| Sense Amplifier                                    |      |

| Peripheral Circuitry                               |      |

| Modeling During Design                             |      |

| MANUFACTURING                                      |      |

|                                                    | _    |

| Processing Steps                                   |      |

| Multiprobe Device Testing                          |      |

| Test Equipment Calibration                         |      |

| QUALITY AND RELIABILITY PROGRAM                    |      |

| Incoming QA                                        |      |

| MOS QRA Program                                    |      |

| Source of Reliability Data                         |      |

| MOS Device Analysis                                |      |

| Electrostatic Discharge Testing                    |      |

| Electrostatic Discharge Testing on Improved Inputs |      |

| MOS QRA Life Test Summary                          |      |

| MOS FAILURE DISCUSSION                             |      |

| MOS FAILURE DISCUSSION                             |      |

| MOSFET Operation                                   |      |

| What is Failure?                                   |      |

| Functional versus Parametric                       |      |

| MOS Failure Mechanisms                             |      |

| Chip-Process Related Mechanisms                    |      |

| Failure Rate Computation                           |      |

| TEST FACILITIES                                    | 20   |

| THE ALPHA PARTICLE CASE                            |      |

| The Problem                                        | 25   |

| The Solution                                       |      |

| THE ROLE OF SYSTEM DESIGN                          | 24   |

| THE RULE OF SYSTEM DESIGN                          |      |

# LIST OF APPENDICES

**Appendix**

Page

| ABCDEFGHIJK | Process Test Flow       32         Assembly Test Flow Diagram       38         TMS 4164 Final Test       41         Quality and Reliability       46         Organization Chart       49         Failure Analysis       51         Manufacturing Support       53         System Test Fixture       56         Portable Alpha Tester       64         Memory System Tester       69         Application Briefs and Specifications       74 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | LIST OF ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Number      | Page                                                                                                                                                                                                                                                                                                                                                                                                                                       |

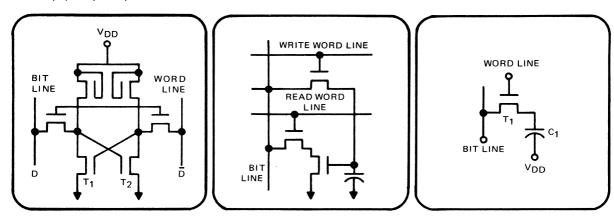

| 1           | 6-Transistor Static RAM Cell                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2           | 3-Transistor Dynamic RAM Cell                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3           | 1-Transistor Dynamic RAM Cell                                                                                                                                                                                                                                                                                                                                                                                                              |

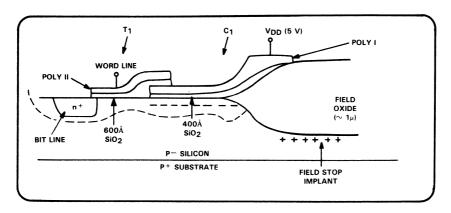

| 4           | Scaled Double Level Poly Transistor Cell                                                                                                                                                                                                                                                                                                                                                                                                   |

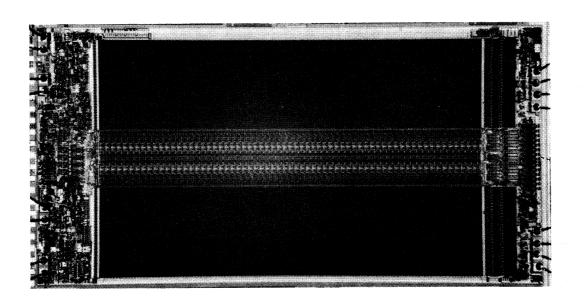

| 5           | TMS 4164 Bar Photograph                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6           | Early Seventies Sense Amplifier                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7           | Typical Sense Amplifier for 16K DRAMs                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8           | Texas Instruments 64K DRAM Sense Amplifier                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9           | CAD Terminal                                                                                                                                                                                                                                                                                                                                                                                                                               |

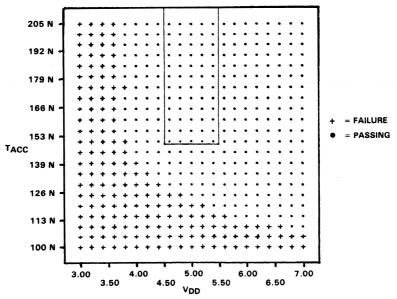

| 10          | Typical SHMOO Plot at 88°C                                                                                                                                                                                                                                                                                                                                                                                                                 |

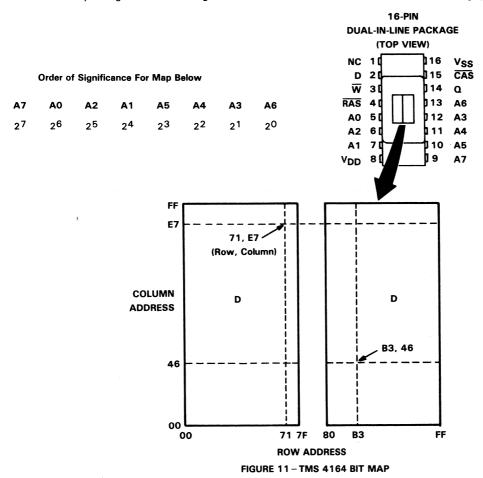

| 11          | TMS 4164 Bit Map                                                                                                                                                                                                                                                                                                                                                                                                                           |

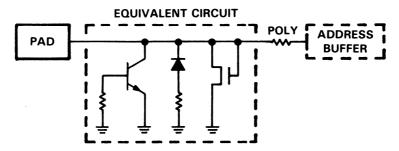

| 11A         | 0.8 MIL Square Diode and 50/3 Micron Metal Gate Field Transistor                                                                                                                                                                                                                                                                                                                                                                           |

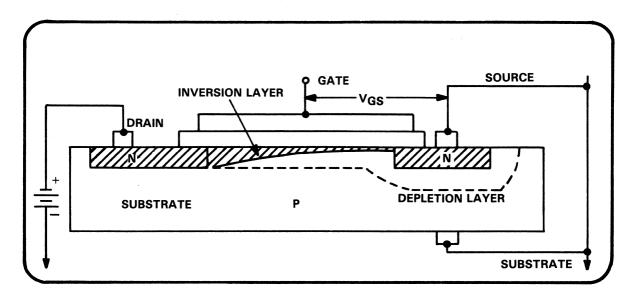

| 12          | N-Channel Enhancement Mode MOSFET                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13          | Characteristic Curve Component Life                                                                                                                                                                                                                                                                                                                                                                                                        |

| 14          | Derating Factors for Various Activation Energies                                                                                                                                                                                                                                                                                                                                                                                           |

| 15          | Higher Derating Factors for Activation Energies                                                                                                                                                                                                                                                                                                                                                                                            |

| 16          | Automatic Memory Tester                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17          | Manual Probe Station                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18          | Scanning Electron Microscope                                                                                                                                                                                                                                                                                                                                                                                                               |

| 19          | Scanning Auger Microprobe                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20          | Alpha Emissions Reduction                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 21          | TMS 4164 with Piq Overcoat26                                                                                                                                                                                                                                                                                                                                                                                                               |

| 22          | TMS 4164 Error Rate Versus Cycle Time                                                                                                                                                                                                                                                                                                                                                                                                      |

|             | LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Number      | Page                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1           | Refresh Times for Single Crystal vs. Epitaxial Silicon                                                                                                                                                                                                                                                                                                                                                                                     |

| 2           | Quality and Reliability Improvement Procedure                                                                                                                                                                                                                                                                                                                                                                                              |

| 3           | Number of Pin Failures                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4           | Alpha Shield Qualification Tests                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5           | Error Comparison                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6           | Mean Time Between Failures                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7           | Hypothetical System Failure Rates                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# TMS 4164 RELIABILITY REPORT

# **ABSTRACT**

This report describes the TMS 4164 Quality and Reliability program at Texas Instruments. Both component and system reliability levels of achievement are presented. Also included in this report are definitions of pertinent quality and reliability parameters to enable the reader to approach these subjects from the same frame of reference as the authors.

The program is a natural outgrowth of Texas Instruments philosophy of system design to achieve customer reliability goals. A long term TI commitment to producing quality components assures our customers that their system will exhibit superior reliability. An example of this continuous effort toward outstanding reliability is the story of the development of TMS 4164 presented here.

#### INTRODUCTION

#### BACKGROUND

The first MOS integrated circuits were produced at TI over 15 years ago. Since that time the N-channel silicon gate MOS process has experienced a long history of high-volume production resulting in a mature, stable, and reliable manufacturing process. This same N-MOS process was selected for the dynamic random-access memory (DRAM)\* family of components because of this fine track record.

The system designer is interested in reliability for several reasons. He usually has requirements imposed on his system that can be met only if the individual components and cumulative design perform within specified limits for predetermined periods of time. These requirements all contribute to the problem that his final decision-making must solve for system reliability. To make the right choices he must know the reliability goals he is designing to and the parameters he must meet.

At this point it is wise to have a firm mental grasp of the impacts of component quality and reliability control. The following definitions should help in clarifying these important concepts.

# **DEFINITIONS**

Quality. The quality of a product is the measure of the degree to which a combination of design and manufacturing expertise conforms to customer requirements at a time baseline we can term "time zero". Quality can be designated as the probability of defective units appearing in a given lot when initially received by the ultimate user. While zero defective items is the ideal goal, there will usually be some percentage of defective units in the lot. The quantity of these units is inversely related to not only quality of design and production that goes into the part but also rigor of the outgoing inspection the part receives.

Reliability. This term is defined as the probability that a unit will operate for a continuous period of time under a given set of operating conditions without failure. Failure is defined as a loss of capability in performing a required function. The time element is the principal difference between quality and reliability. Reliability is, in effect, a measure of how long quality lasts.

System Reliability. This, in the field, is a function of the total reliability of system components and the design implementing these components. Present large-scale integration techniques relieve today's system designers of many reliability concerns by providing "systems on a chip" with built-in reliability. Much of the system reliability concern is then shifted to the component design process. This subject will be discussed further on.

It is well known that the higher the level of device integration, the lower the failure rate on a per-function basis. The reduced interconnection requirement results in fewer wirebond and other such age-related failures. Many systems exhibit series reliability and, assuming a constant component failure rate, can be calculated by simply adding the individual component failure rates. System reliability considerations are covered in more detail in the Quality and Reliability Program section.

Component Reliability. Systems designers are concerned with the contribution of each component to the system failure rate. The component reliability is frequently expressed as a rate (percent per 1000 hours, FITs failures per 10<sup>9</sup> hours etc.) or a time such as MTBF (mean time between failures). The ultimate consideration, however, is its impact on the system. This may be a question of contribution to systems during warranty, system field repair intervals, etc. We will discuss later, in some detail, the significance of component reliability and the factors involved in current advanced LSI technologies.

Achieving high quality and long-term reliability in any product costs money, manpower, and time. The amount of money is related to the production rate, design reliability goals, and equipment necessary to measure progress in achieving the desired goals. The personnel involved must be dedicated to quality and interested in how their job functions impact on final test processes and device tests. Time is required both to develop a history of reliable processing and to produce the actual quality and reliability data that is needed to project future reliability goals.

<sup>\*</sup> Dynamic random-access memories, (DRAMs) also known as read/write memories, are today's most widely used, efficient memory devices in large main-frame, minicomputer, and microcomputer systems. They have successfully replaced magnetic core memories as the medium for main memory storage since the early seventies.

#### MEMORY DESIGN

#### **BACKGROUND**

Quality must begin before the first wafers are processed. Reliability is a result of a history of designing-in quality. The evolution of dynamic RAMs is a story of the MOS technology coupled with innovative circuit design techniques. On-chip address translation and decoding with TTL-compatible input/output circuitry make the present day N-channel, silicon gate, 5-volt-only 64K DRAM, such as the TMS 4164, easy to use in any kind of memory-intensive system.

# **CELL**

The 6-transistor flip-flop of the late sixties was the basic cell used in static RAMs. Although there are a few variations of this cell, e.g., depletion loads, poly-resistor loads, etc., the static RAM cells of the early eighties maintain these characteristics. The DRAM cell gradually evolved from the 6-transistor cell (Figure 1) to the 3-transistor cell (Figure 2) and finally the 1-transistor cell (Figure 3). The 3-transistor cell was used in the P-channel silicon gate 1103 DRAM (1024 words × 1 bit), the first popularly accepted DRAM.

FIGURE 1 – 6-TRANSISTOR STATIC RAM CELL

FIGURE 2 - 3-TRANSISTOR DRAM CELL

FIGURE 3 - 1-TRANSISTOR DRAM CELL

As proven by the 4K DRAM (TMS 4030, TMS 4060, TMS 4027) and later the industry standard 16K DRAM (TMS 4116) and 64K DRAM (TMS 4164), the basic 1-transistor/1-capacitor cell has become the workhorse for data storage. The operation of this cell is described below.

Transistor T1 is designated the access transistor or transfer gate, and it acts as a 2-way switch to propagate data to or from the bit line to the storage capacitor, C1. C1 is a conventional MOS capacitor whose field plate is connected to a fixed positive potential V<sub>DD</sub> (nominally 5 volts) as shown in Figure 4. This figure depicts a scaled double level poly-transistor cell. The poly-1 field plate connected to V<sub>DD</sub> drops enough potential across the SiO<sub>2</sub> dielectric to form an inversion layer in the silicon underneath the electrode.

FIGURE 4 - SCALED DOUBLE LEVEL POLY-TRANSISTOR CELL

When a true logic "0" is to be stored, the n+ diffused bit line is brought to VSS (0 volts), and the access transistor, T<sub>1</sub>, is turned on (V<sub>DD</sub>+). The storage node, which is at the Si-SiO<sub>2</sub> interface, is discharged to VSS. When the word line is brought to V<sub>SS</sub>, the storage node remains filled with electrons (minority carriers for an N-channel RAM). Conversely, if a logic "1" were to be stored, the bit line would be brought to V<sub>DD</sub>, thus depleting all the electrons at the storage node. During store, the word line potential is not expected to ever exceed one threshold voltage above V<sub>SS</sub> for unselected word lines. (Reliable operation of the RAM demands very quiet word lines. Active bleeder devices in TMS 4164 hold the unselected word lines at ground potential during the critical sensing amplification period.) Minimal sub-threshold leakage through the transfer gate is also assured in TMS 4164 by precharging the bit lines to V<sub>DD</sub>, thus supplying the most positive voltage available on the source node of the access device. Use of epitaxial silicon for the top several microns of substrate ensures excellent refresh times under worst-case operating conditions.

# **SENSE AMPLIFIER**

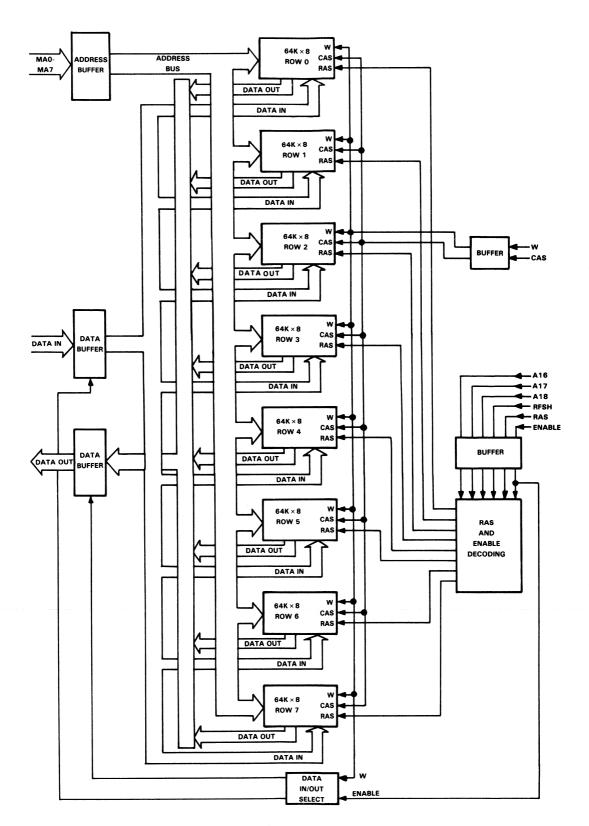

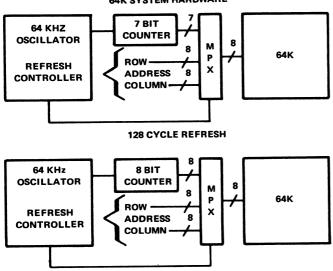

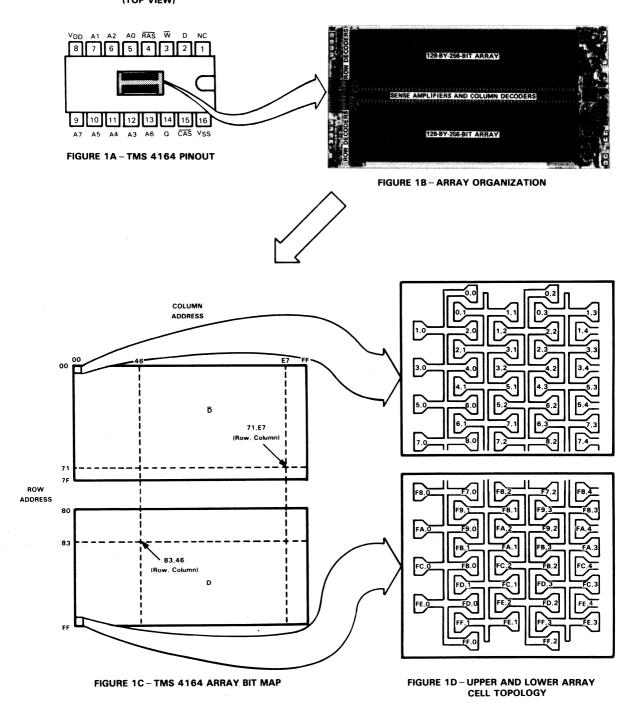

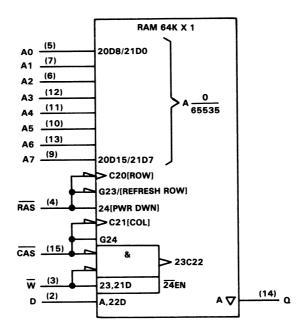

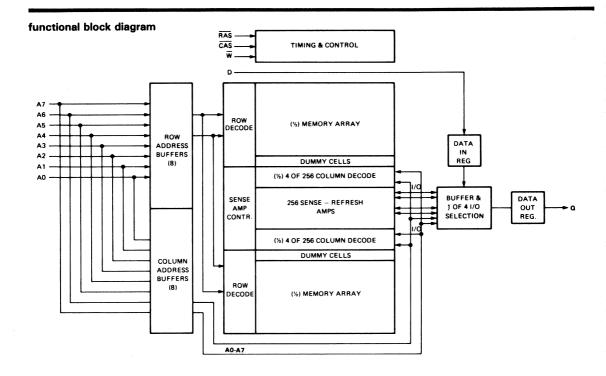

With added complexities and large densities, effective sensing circuitry has become mandatory for reliable memory operation. In TMS 4164 the 8-row addresses provide a 1-out-of-256 row selection and the 8-column addresses provide 1-out-of-256 column selection. The 64K dynamic RAM is optimally organized as a 256-row × 256-column matrix to operate the chip at minimal power dissipation (enhancing system reliability through relatively cooler chip temperature). The on-chip circuitry, including decoders, clocks, etc., is shown in Figure 5.

FIGURE 5 - TMS 4164 BAR PHOTOGRAPH

The basic detection circuitry is a dynamic differential amplifier. This amplifier is expected to detect a signal as small as 100 millivolts worst-case (C-storage/C-bit line is approximately 0.07 in TMS 4164) and amplify this signal by a factor of 50 in less than 30 nanoseconds. In addition the differential amplifier must dissipate less than 0.1 milliwatt in any given cycle (25.6 mW per device).

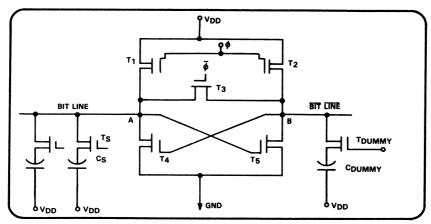

The sense amplifier, popular in the early seventies, is a static differential amplifier shown in Figure 6. The bit lines are precharged to  $V_{SS} + V_{T}$  and are equalized through transistor, T3. The dummy storage capacitance,  $C_{dummy}$ , is about  $C_{S}/2$ . The word line for the selected bit and the dummy bit are on the opposite side of the differential amplifier between the two bit lines (whether "O" or "1" is read out of the bit). A small differential voltage is established on the bit lines when the storage all transfer gate,  $T_{S}$ , and the dummy cell transfer gate,  $T_{dummy}$ , are turned on. The loads T1 and T2 are activated, and the amplification process is completed through the flip-flop action as with a conventional static flip-flop.

FIGURE 6 - EARLY SEVENTIES SENSE AMPLIFIER

The disadvantages of this amplifier are excessive power dissipation (amplifier has a dc path almost all the time when CE is high or  $\overline{RAS}$  is low), direct loading of bit line capacitance on sensing nodes A and B and excessive bit line capacitance (precharge to VSS only CJN  $\alpha$  (VJN)-1/2. These problems have been partly solved in early 16K DRAM designs. A typical sense amplifier used in I6K DRAMs is shown in Figure 7.

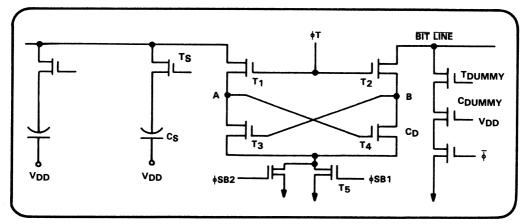

FIGURE 7 - TYPICAL SENSE AMPLIFIER FOR 16K DRAMS

The dynamic sense amplifier shown above isolates the large bit line capacitance from the sensing nodes A and B by means of isolation devices T1 and T2 thus speeding up sensing action. By modulating phase  $\phi_T$ , T1 and T2 offer high impedance in pre-sense and low impedance in post-sense action. Bit line capacitance is reduced by precharging bit lines to  $V_{DD}$ . The activation of amplification circuitry is accomplished through a 2-step sequential activation of phase SB1 and phase SB2. Although this sense amplifier, when compared to the amplifier shown in Figure 6, conserved power and sped up the overall sensing process, it lacked an effective method of writing a full "1" level back into the storage node when "1" is read out or written in. This is accomplished in the sense amplifier used in TI's 64K DRAM (U.S. Patent 4, 239, 993). The key elements are shown in Figure 8.

FIGURE 8 - TEXAS INSTRUMENTS 64K DRAM SENSE AMPLIFIER

Note that restoring full "1" level:

- (1) Enhances refresh time and inherent design margins

- (2) Gives capability for extended page operation

After sensing, dynamic loads are activated. This minimizes "bump" on active low-going bit lines, conserves average power, and lowers IDD transient peaks. The selected word line is booted above VDD while restoring the read datum.

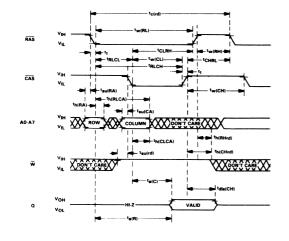

#### PERIPHERAL CIRCUITRY

For better component reliability and avoidance of timing glitches internal to the chip, the on-chip clock design on TMS 4164 uses a novel interlock system. While the older-generation DRAM on-chip clock generators relied entirely on gate delays, and thus were susceptible to internal race conditions, TMS 4164 employs interlock clock schemes that render the working chip relatively immune to parametric variations in the manufacturing process. For example, until the word line decoding has been completed, the word line (to the access transistors) will not be activated. This technique also helps to reduce IDD peaks to less than 70 milliamperes (typically).

The TMS 4164 is designed with separate on-chip address buffers for row and column address detection and subsequent voltage amplification (minimum TTL levels to full  $V_{DD}/V_{SS}$  internal to the chip). Use of separate address buffers eliminates the need for complex multiplexing and clocking circuitry, and also provides increased margins for address setup and hold times. An on-chip finely-tuned reference generator coupled with very sensitive 3-stage dynamic input differential amplifiers allow accurate, quick address level detection. Use of epitaxial silicon provides an excellent sink for minority carriers within a few microns (far less than 1 diffusion length). This enables the TMS 4164 to tolerate typically -1 volt dc levels, and up to -3 volt transients on inputs. Series poly resistors and N+/P- junctions at the bondpads (addresses) provide adequate filtering action and level capture.

#### **MODELING DURING DESIGN**

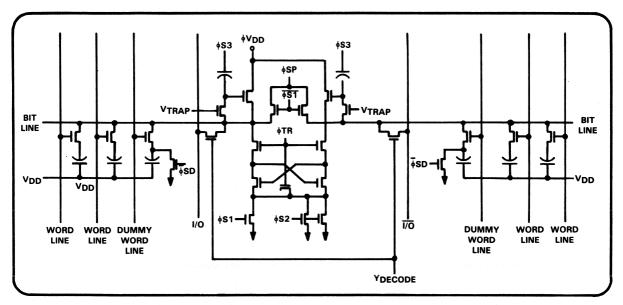

The design is not complete with the circuit description and electrical schematic. Using the desired propagation delays and circuit description, the logic is modeled for proper device operation using various computer simulations. When logic has been verified, the design is then adapted to simulation programs that calculate device performance based on the capacitance and resistances involved in the various process materials. These programs comprehend process variations which the designer must account for (VT windows, poly widths, etc.) and then suggest the required layout of logic on the actual chip to maximize speed performances and minimize noise and power providing high quality and reliability. The simulation programs are linked to Computer Aided Design (CAD) stations (Figure 9) where actual layout of the device is generated. Each of the masks used in wafer fabrication is stored on tape and may be modified or updated at the CAD station.

#### **MANUFACTURING**

#### PROCESSING STEPS

A detailed description of the manufacture of the TMS 4164 is not practical in this report; however, the ultimate quality of the part is a direct result of the way in which it was fabricated. Consideration of some of the processing steps and their effects serves to demonstrate this relationship.

One of the unique features of the TMS 4164 is that it is fabricated on a lightly doped P - epitaxial silicon layer grown on a heavily doped P + substrate. The heavily doped P + substrate provides the following:

- (1) Highly conductive ground plane that minimizes noise coupling into critical sensing circuitry from the input pads when inputs are allowed to swing from V<sub>IHMAX</sub> to V<sub>ILMIN</sub> (almost an 8-volt swing in less than 5 nanoseconds). Other sources of noise are similarly damped.

- (2) Relatively inferior charge lifetime so as to be an excellent minority carrier sink

- (3) Excellent backside contact in package minimizing sensitivity to complex data patterns

The lightly doped P - epitaxial layer provides:

- (1) Relatively high minority carrier lifetime, guaranteeing excellent data storage time for the array (translates into long refresh times at elevated temperature)

- (2) Relative freedom from heavy metallic contents, minimizing undesirable array/peripheral leakages (junction, field-induced)

The interface of the P – /P + substrate furnishes a good minority carrier sink due to an interface with a large gradation of impurity concentration variation. (MOS, being a surface-oriented device, requires a very high quality 2 to 3 micron deep region underneath the field plates and junctions.) These attributes of TMS 4164 give it an excellent tolerance to data patterns and assure data integrity under worst-case voltage/temperature input conditions. Figure 10 shows a typical Shmoo plot highlighting extreme tolerances to input level swings beyond the data sheet specifications at 88°C. Table 1 demonstrates the advantages of epitaxial silicon in preserving long refresh times even at 90° case temperatures. The table gives typical refresh times for TMS 4164s constructed under the same process and design rules with the only difference being the EPI layer on one group. It can be seen from this data that a significant improvement in refresh times is shown in the EPI crystal.

Another advantage of the epitaxial layer is enhanced performance of the diffused guard rings. These rings are diffused around each array half and are biased to V<sub>DD</sub> during operation. This creates a depletion region around the arrays making it nearly impossible for minority carriers to penetrate. Empirical data shows that this guard ring is at least five orders of magnitude more effective using the epitaxial layer versus a homogeneous crystal substrate.

FIGURE 10 - TYPICAL SHMOO PLOT AT 88°C

TABLE 1 - REFRESH TIMES FOR SINGLE CRYSTAL VS. EPITAXIAL SILICON

|                     | SINGLE CRYSTAL |              |                   | EPITAXIAL |              |  |

|---------------------|----------------|--------------|-------------------|-----------|--------------|--|

| UNIT BURST (ms) DIS |                | DISTURB (ms) | DISTURB (ms) UNIT |           | DISTURB (ms) |  |

| Α                   | 318            | 6            | Α                 | 502       | 92           |  |

| В                   | 234            | 4            | В                 | 1000      | 132          |  |

| С                   | 184            | 4            | С                 | 600       | 57           |  |

| D                   | 247            | 4            | D                 | 520       | 111          |  |

| E                   | 196            | 8            | E                 | 430       | 87           |  |

| F                   | 14             | 4            | F                 | 241       | 56           |  |

NOTE: T<sub>case</sub> = 90°C.

Enhanced oxide reliability has been accomplished in TMS 4164 wafer fabrication process with the use of lower (relatively) temperature thermal oxidation in a carefully controlled HCL oxidation growth process. Minimizing the exposure of the critical gate insulator to organic/inorganic elements/chemicals prior to highly pure polysilicon deposition enhances the long-term system reliability by reducing time-dependent gate oxide ruptures and mobile ionic contamination presence in a carefully controlled environment. Nominal  $3\mu$  poly leads are etched with dry processing techniques to ensure tight physical geometry/electric parameter control. Low phosphorus concentrations in multilevel doped insulator minimizes metal corrosion at high humidity operation. Sputtered silicon-doped aluminum covering smoothly "reflown" oxide steps coupled with low power dissipation (less than 100 milliwatts at system cycle operation) minimizes electromigration and keeps the chip relatively cool.

#### **MULTIPROBE DEVICE TESTING**

Before dividing the wafer into individual devices, it is electrically tested via probes. The wafer probe operation is the first functional testing of the memory. This three-fold test accomplishes the following:

- (1) Eliminates non-functional devices that, if assembled, would not meet the rigid requirements of back end final test.

- (2) Provides the product engineer with actual parametric characteristics that are a function of the front end (fabrication) process. This is accomplished by providing test sites for such transistors, capacitors, continuity and leakage structures. These sites are related to the devices used in memory periphery and array.

- (3) Provides characterization of the memory device itself by finding minimum and maximum operating parameters.

This is done typically on a sample basis and gives immediate feedback to process/product engineering.

The functional devices from probe are then assembled (see Appendix B) before final testing.

Testing the TMS 4164 has evolved from earlier DRAM testing including the TMS 4116 program. After comprehending additional addresses, the same pattern and data sequences can be applied to the TMS 4164 as were applied to the TMS 4116. However, the device has developed its own characteristics that require customized programs with unique patterns. These test patterns guarantee a quality device while incurring a minimum of test time.

The patterns used in production are those determined from the internal logic and layout to produce the greatest possibility of failure detection. These tests cannot make up a truly comprehensive pattern test of memory array as there are 265,536 possible data patterns. Subsets of these patterns can be located to ensure that pattern sensitivity does not exist in the part, and that certain locations are not unduly susceptible to noise on control, address, or power pins.

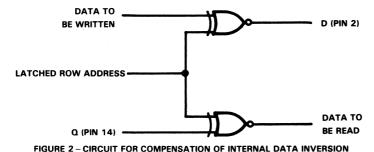

The bit map of the TMS 4164 (Figure 11) suggests more testing considerations as the data to one of the two halves of the device array is inverted. The identification of memory failure mode is dependent on this type of information. The test flow and test descriptions are in Appendix C. A bit map of the TMS 4164 can be obtained using the true address bit significance as shown in Figure 11.

When a product is in its infancy, the correlation of final test failures to multiprobe testing is handled differently from the correlation of a mature device. During product development, the product engineer must optimize the total number of devices with little regard for assembly and test costs. As a product reaches maturity, a stringent multiprobe test optimizes final test yields thus reducing back end costs. This becomes important in high-volume production devices, such as DRAMs, where a significant portion of the final cost is directly related to assembly and test yields.

Texas Instruments has the capability for special test flows for those customers who require particular device functionality beyond typical operating parameters. These special test flows may include additional burn-in testing for reduced near-term failure rate or testing for operation outside the normal electrical or temperature range. Each of these flows is assigned a number. Parts passing these tests are given this number in addition to normal device markings.

Data on the left half of the array (as shown above) is stored in inverted form (1 = absence of charge) while data on the right half is stored in true form (1 = charge). Therefore, row address bit 7 is the bit that selects between the true and inverted array.

# **TEST EQUIPMENT CALIBRATION**

To ensure that the product is tested accurately, a Quality Control (QC) procedure has been established for device testing equipment. This is a special set of diagnostic routines that are unique to the TMS 4164 and are in addition to the normal maintenance of the test equipment. These routines include:

- Maximum edge accuracy in all timing signals (This eliminates address skew and insures compare strobe integrity, etc.)

- (2) Driver voltage accuracy to insure precise VIL and VIH levels

- (3) Power supply accuracy

- (4) Handler temperature accuracy

- (5) Test contact resistivity, leakage

These diagnostics are performed prior to Quality Assurance (QA) acceptance procedures during each production shift.

#### QUALITY AND RELIABILITY PROGRAM

#### **INCOMING QA**

Just as our customers need quality components to build reliable systems, TI must require that the materials and equipment we use provide the necessary quality to our products. For that purpose Texas Instruments maintains an effective incoming material control on all production material and parts that become a part of or are consumed in the manufacturing process. The tests and evaluations performed include inspections of mechanical, physical, dimensional, functional and electrical characteristics as specified in the TI documents that are supplied to the vendor with the purchase orders. For example, vital to TMS 4164 reliability is the control of mold compounds for the plastic encapsulation process. Texas Instruments maintains strict incoming material control to guarantee proper chemical formulation, molding characteristics and properties of the molded material. A preshipment sample of each lot of mold compound must pass incoming QC before the vendor is allowed to ship the lot. Upon passing incoming inspection, an acceptance number is assigned to the lot of mold compound and communicated to the vendor and to TI molding operations worldwide. In addition, comprehensive material specification and inspection procedures are maintained to assure consistency in moldability and reliability.

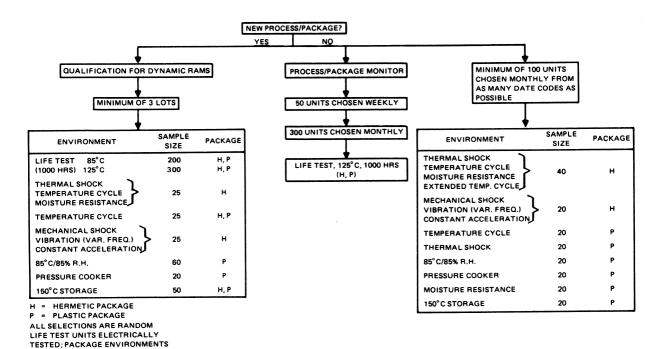

#### MOS QUALITY AND RELIABILITY ASSURANCE (QRA) PROGRAM

The production flow for dynamic RAMs is shown in Appendices A and B. Built-in reliability is guaranteed by stringent process controls, in-line monitors of critical parameters, and rigid acceptance procedures of pieceparts. Various analytical instruments are utilized to monitor processes, trouble-shoot manufacturing process problems, and perform engineering evaluations. This approach assures optimum control of etch times, diffusions, metallization clean-ups, etc. Control charts are maintained on parameters, such as oxide and film thickness, junction depths, topological geometries, and electrical parameters. High temperature and voltage stress samples are evaluated on a skip lot basis. These tests with pre- and post-stress measurements evaluate the process stability and provide control with early corrective action feedback.

#### **SOURCE OF RELIABILITY DATA**

Reliability data is collected by following the QRA flow for dynamic RAMs (see Appendix D).

By executing the evaluations in a rigorous and thorough manner current and accurate electrical and mechanical data are obtained. This data indicates the reliability status of the manufacturing processes in an ongoing basis. Analysis of the reject units provides the information for corrective action and continued improvements. New devices, packages, production sites or revised processes are thoroughly tested via the left-hand leg of the flowchart shown in Appendix D. Thus product worthiness is proved before volume commitments are made. As required, additional testing by TI or by the customer may also be performed. Shared data and analysis further adds to the experience base for quality and reliability improvements.

Ensuring that TMS 4164 shipments are of the highest quality and reliability is our primary goal; however, we want our customers to benefit the most from our efforts. Consequently, TI provides customer support after the parts are shipped (see Appendix K). We combine our knowledge of how the devices work with expertise in system design to help customers improve system reliability.

#### **MOS DEVICE ANALYSIS**

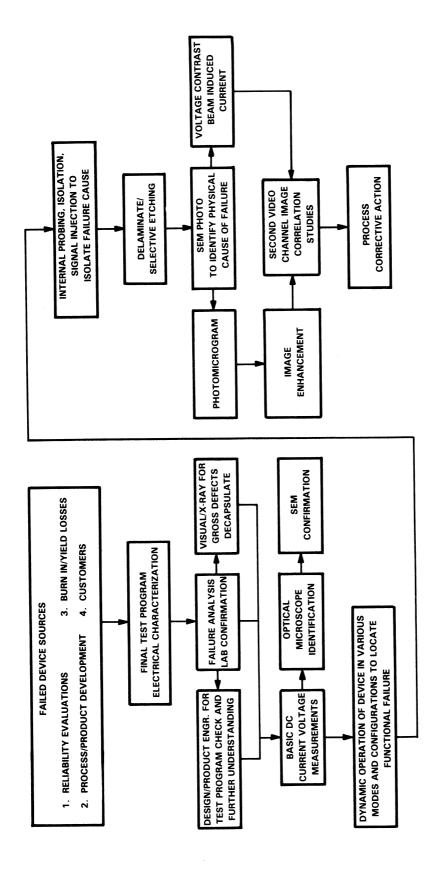

The importance of quality and reliability improvements are reflected in the number of techniques and amount of resources that are dedicated to this effort. At Texas Instruments these resources have been increased at a very significant rate over the past few years. Recommended procedures in the quality and reliability improvement program are shown in Table 2. Further support in solving the problem and cause is furnished by the failure analysis flow given in Appendix F. This flow not only shows the thought or decision process but also includes the equipment used and a projected cycle time.

#### TABLE 2 - QUALITY AND RELIABILITY IMPROVEMENT PROCEDURE

#### The PROBLEM

The problem must be described and quantified in specific terms.

#### The CAUSE

The cause must be identified and defined as accurately as possible based upon the available information.

#### SHORT TERM ACTION

Identify the immediate action to be taken to limit the problem and the effective date of the action.

#### LONG RANGE ACTION

Show the planned action and effective date for permanent problem correction.

#### VERIFICATION

Measure the effectiveness of the actions by indications that chart problem severity. Actions are not considered complete until indicators show effective resolution.

#### OUTLOOK

Project the long range effect of the problem and corrective actions. State the degree of confidence in the effectiveness of the actions.

#### COST

Account for total cost of corrections.

# **ELECTROSTATIC DISCHARGE TESTING**

Occasionally special testing is done to comply with specific requirements of the customer. An example of this testing service is described next.

Tests have been performed on 30 TMS 4164 parts to determine the effects of various levels of electrostatic discharge on the functionality of the devices. The 30 units were tested in three groups of 10 units each. Group #1 was tested with increasingly positive electrostatic discharge voltage (VESD). Group #2 with increasingly negative VESD. Group #3 was further separated into five subgroups of two and each of these was repetitively tested at a different VESD.

Testing consisted of applying a 150 pF capacitor charged to a specific VESD ranging from  $\pm$  400 to 700 volts through a 2.2K $\Omega$  resistor to the pin under test (PUT). All voltages and currents were referenced to pin #16 (VSS). PUT was then checked for leakage and continuity. A pin failed the leakage test if the current exceeded 10 microamperes when -5.5 volts was applied. PUT failed the continuity test if it required more than +1.5 volts to force 80 microamperes into it.

Each device in Group #1 was tested at 400, 450, 500, 600, 700 volts. The devices in Group #2 were tested in the same manner but using negative voltages. Each subgroup of Group #3 was tested 20 times at one of the following V<sub>ESD</sub>s: 450, 500, 550, 600, 700 volts. Once any given PUT failed, it was skipped in succeeding test repetitions.

The results are tabulated below:

**TABLE 3 - NUMBER OF PIN FAILURES**

| GROUP # | TYPE OF<br>FAILURE | 700 V | 600 V | 550 V | 500 V | 450V | 400 V |

|---------|--------------------|-------|-------|-------|-------|------|-------|

| 1.      | CONTY              | 8     | 3     | О     | 0     | 0    | 0     |

|         | LEAKAGE            | 8     | 0     | 0     | 0     | 0    | 0     |

| 2.†     | CONTY              | 33    | 6     | 3     | 0     | o    | 0     |

|         | LEAKAGE            | 3     | . 1   | 0     | 0     | 0    | 0     |

| 3‡      | CONTY              | 20    | 20    | 23    | 11    | О    | _     |

|         | LEAKAGE            | 4     | 2     | 0     | 0     | 0    | -     |

<sup>&</sup>lt;sup>†</sup> Negative V<sub>ESD</sub>

# **ELECTROSTATIC DISCHARGE TESTING ON IMPROVED INPUTS**

Improved input protection circuits have been subjected to electrostatic discharge testing which indicate that the circuit will withstand ESD voltages greater than 2000 volts. The improved input protection circuit shown in Figure 11A will be implemented on the TMS 4164A and the TMS 4416 in late 1982.

FIGURE 11A - 0.8 MIL SQUARE DIODE AND 50/3 MICRON METAL GATE FIELD TRANSISTOR

Testing consisted of applying a 150 pF capacitor that was charged to a specific V<sub>ESD</sub> from  $\pm$  500 volts to  $> \pm$  4000 volts through a 1.5K $\Omega$  resistor to the pin under test (PUT). All voltages and currents were referenced to pin 16 (V<sub>SS</sub>). PUT was then checked for leakage and continuity. A pin failed the leakage test if the current exceeded 1 microampere when -5 volts was applied. PUT failed the continuity test if it required more than +1.5 volts to force 80 microamperes into it.

# MOS QRA LIFE TEST SUMMARY

Accelerated life testing is performed routinely on random samples of prototype and production units. Shown below is a summary of all life testing on plastic parts for the first three quarters of 1982.

| TEST<br>°C | QTY   | REJ | ACTUAL<br>DEV HRS | DEV HRS<br>@ 55°C | FITS*<br>60% UCL |  |

|------------|-------|-----|-------------------|-------------------|------------------|--|

| 125        | 5,419 | 35  | 4,861,700         | 109,000,000       | 341              |  |

<sup>\*</sup> FITs or Failures in Test reflect the number of failures in  $10^9$  device hours (1 FIT = 1 failure per  $10^9$  device-hour).

<sup>‡</sup> Repeat 20 times or until failure

#### MOS FAILURE DISCUSSION

# **MOSFET OPERATION**

An N-channel enhancement-mode MOSFET is illustrated in Figure 12. The three terminals identified are the source (reference terminal), the gate (control electrode), and the drain or device output. These terminals may be roughly compared to the bipolar's emitter, base, and collector. With the substrate source and gate grounded, and the drain held at some positive potential, the reverse biased drain-to-substrate PN junction prevents drain-to-source current flow.

FIGURE 12 - N-CHANNEL ENHANCEMENT MODE MOSFET

The gate electrode controls charge in the substrate "channel" between source and drain. When a negative voltage (with respect to the source) is applied to the gate terminal, free electrons in the silicon substrate between drain and source are repelled forming an accumulation region of holes. Positive bias attracts electrons to this region until an inversion layer or a negative conductive channel between N-type source and drain forms. The voltage required at the terminal to form channel inversion is referred to as threshold voltage of V<sub>T</sub>.

Since source and drain are virtually interchangeable, channel current can flow in either direction. The MOSFET, therefore, becomes an ideal switch, capable of bilateral current flow with an almost infinite off impedance.

A few additional words should be included here concerning MOS capacitance. The input terminal of the MOSFET, in combination with the gate-oxide insulator and silicon substrate, form a voltage-dependent capacitor. This gate capacitance is particularly important for in-process studies of oxide-layer properties, e.g., contamination in the oxide and its effects on the oxide-silicon surface characteristics. Threshold voltage and oxide properties are vital to understanding MOS failure mechanisms.

#### WHAT IS FAILURE?

A device failure is defined as the cessation of ability to perform a specified function or functions within previously established limits. This requires that measurable limits be defined to describe satisfactory performance. Most users are concerned with the overall performance of the system in the hands of the ultimate consumer. Small shifts in device parameters are possible, but these are usually insignificant and do not contribute to degraded performance at the system level. While the designer has control over a conservative system design, he must anticipate the intended working environment.

#### **FUNCTIONAL VERSUS PARAMETRIC**

A functional failure may be one that is termed catastrophic or totally non-operable or one that lacks at least some degree of functionality. The functional failure may be either chip or package-related but is usually the result of a manufacturing defect or improper use in the hands of a customer. Parametric failures are those that involve an electric parameter or parameters that no longer meet a guaranteed data sheet limit. In many cases these "failures" will continue to function properly in a well-designed system. Parametric failures are usually chip-related or involve an interaction of package and chip. Diffusion leakage, MOS surface leakage currents, and shifts in threshold voltages are all examples of failure modes that may contribute to parametric failures. These effects may manifest themselves as input/output leakages, reduced drive capability, skewed oscillator frequencies, etc. The primary concern of parametrics is the indication of a processing problem that may degrade with time to a functional failure as defined by system requirements. All semiconductor products will experience certain changes in electrical parameters with time. It is only those showing a rapid shift to "out of spec" tolerances that concern the component reliability engineer and system user.

#### MOS FAILURE MECHANISMS

MOS memory failures that occur after comprehensive electrical testing result mostly from processing flaws that exist in the chip or package. Chip-processing related defects control the failure rate in the case of the TMS 4164. Because of this, it is necessary to understand and control the MOS chip-processing facilities and variables critical to reliability. Included below is a brief summary of failure mechanisms that can contribute to reduced MOS product reliability.

#### **CHIP-PROCESS RELATED MECHANISMS**

Mobile Ions (Parametric Drift). All oxides are sensitive to ionic contamination, which will migrate in the oxide under electrical and thermal stress. The predominant effect of excessive contamination in gate oxides is a shift in the threshold voltage after application of voltage and temperature. Under such conditions, negative gate voltages attract positive charge to the gate electrode and drive negative charge to the oxide-silicon interface.

*Electrochemical Corrosion.* The corrosion of aluminum metallization may be caused by excessive moisture penetration and/or residual chemicals on the chip surface. This is manifested by high-impedance leakage, an open connection, or loss of ohmic contact. Attention to cleanliness, packaging materials, and the packaging process control reduces this hazard.

Metal Cracks. Improper oxide contours resulting from incorrect thickness or procedure allow a thinning of metallization and cracking at extreme steps. A Scanning Electron Microscope metallization monitor controls the process for out-of-tolerance aluminum coverage.

Oxide Defects. Oxide defects in the gate and field insulators can be particularly troublesome to device operation. These defects are categorized by pinholes, scratches, and undercutting. A pinhole is an isolated region where the dielectric has broken down. When this occurs, a short to the silicon substrate is created. Scratches in field oxide may result in incomplete diffusion masking during later stages of processing. Oxide undercutting results in an increase in dimensions of an oxide window during oxide removal. When excessive, this can lead to latent failure modes. The utmost care and control of oxide operations is necessary to guarantee high reliability since these areas are some of the most critical to long-term device performance.

Inversion (Spurious MOSFET Leakage). Since turn-on voltages of most MOSFETs in application are dependent upon the potentials of source and drain as well as the inherent V<sub>T</sub> of the device, it is frequently necessary to apply gate voltages well above the device V<sub>T</sub>. Under certain conditions this voltage is sufficient to cause inversion under thick-field oxides resulting in the establishment of current paths between N-type diffusions and loss of isolation. This problem can be caused by thin field oxide or decreased oxide charge associated with the thick oxide. These effects are also created by lateral charge spreading from high-voltage nodes along the surface of the field oxide. A process control technique has been developed to detect lateral charge spreading tendencies in lots where insufficent cleanups allow ionic contaminants to migrate and form unwanted field inversions.

Diffusion Leakage. Diode leakage can result from irregular oxide photoengraving prior to source-drain diffusion resulting in irregular diffusion profiles. Defects in the starting silicon material, if located in the depletion region of source or drain diffusions, may also cause anomalies in diode characteristics. Careful slice handling and the avoidance of extreme temperatures during processing contribute to the decreased defect levels in substrate silicon.

Thermocompression Bonding Failures. The gold-aluminum bonding system employed in MOS processing is subject to formation of gold-aluminum intermetallics and voiding when subjected to uncontrolled high temperatures. This voiding, if severe, can lead to high-resistance bonds and ultimately to lifted bond wires. The formation of these compounds has been minimized by using strict temperature controls during fabrication and by limiting operating temperature to 125 °C or less and storage temperature to 150 °C.

Header/Materials Failures. Package failures can result from faults with the ceramic header or lead frame. Poor plating can result in lifted bonds at the post. Open metallization within the ceramic header can cause lack of continuity to the bar and result in electrical failure. If the plastic encapsulation material processes are not properly controlled, failure can result after exposure to the intended environment. Improper coefficients of expansion and contraction can cause lifted or broken bond wires after extended thermal cycle. A high content of mobile ionic contamination in the plastic can create MOS surface leakage problems or contribute to aluminum corrosion tendencies when exposed to high humidity environments. TI has devoted significant resources to develop the proper plastic for MOS use and maintains stringent controls on incoming materials and the encapsulation process.

Chip Damage. Chip cracking can occur during the assembly process and result in latent failures. The cracking may occur around the periphery of the chip, through the active area of the circuitry, or emanate from the bond pads. Cracks around the periphery may be induced during scribe and break. These cracks may propagate to areas of active circuitry after exposure to later processing stresses. Cracks radiating from bonding pads result from thermal or mechanical stresses induced during thermocompression ball bonding. Bond pad cracks can be a threat to reliability since they may be concealed by ball bond and bonding pad.

# **FAILURE RATE CALCULATION**

An understanding of the reliability capabilities of a system in terms meaningful to the user requires a basic knowledge of component and system failure rate calculations and the treatment of accelerated test data.

Suppose the cumulative distribution of the life of a given item is Q(t). In other words, the probability that an item will have a life of t or longer is 1-Q(t). This survival probability is called the reliability, designated by R(t) = 1-Q(t). If an item has survived for a time t, the probability it will fail in the next t time units is

$Q(t+\triangle t) - Q(t) = [1-R(t+\triangle t) - (1-R(t))]$  $= -R(t+\triangle t) - R(t)$

If we take

$\frac{\ell im}{\triangle t \rightarrow 0} - \sum \frac{[R(t + \triangle t) - R(t)]}{\triangle t} = \frac{dQ(t)}{dt} = q(t)$

we get the density function of the distribution of life Q(t):i.e.,

$$\frac{dR(t)}{dt} = -q(t) \bullet$$

If we divide q(t) by R(t), we get the "instantaneous failure rate" or "hazard rate". Therefore, if one started with N items, all operating under identical conditions, then by the time t, we would have on the average NR(t) left. During the next time interval,  $\Delta$  t, there would, on the average, be

$$\frac{dQ(t)\triangle t}{dt} = -\frac{dR(t)\triangle t}{dt}$$

failures and the failure rate or number of failures during At per number of survivals at time t is

$$\frac{-dR}{dt} \; \frac{\triangle t}{R(t)} \; \bullet$$

This is the instantaneous failure or hazard rate  $\lambda(t)$

$$\lambda(t) = \frac{-1}{R(t)} \frac{dR(t)}{dt} = \frac{q(t)}{R(t)} \bullet$$

The reliability function is then given by:

$$R(t) = Ke^{-\int_{0}^{t} \lambda(t)dt}$$

where K is a proportionality constant.

If  $\lambda(t)$  is assumed constant, then

$$R(t) = Ke^{-\lambda(t)}$$

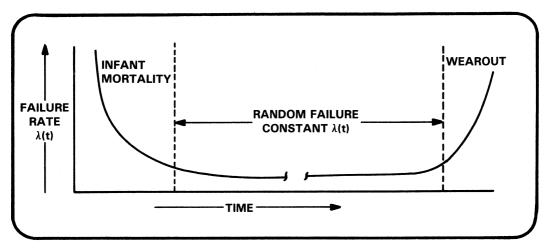

and the failure rate is described by device failures occurring randomly in time. It is well known that semiconductors typically follow a "bathtub" curve in the infant mortality and constant failure rate regions when failure rate is plotted versus time. Wearout is not normally observed in system use but can be produced by highly accelerated testing techniques. This is shown in Figure 13.

FIGURE 13 - CHARACTERISTIC CURVE COMPONENT LIFE

The infant mortality portion of this curve defines the time during which a portion of the product containing manufacturing defects fails at excessive levels. These "freak failures" are superimposed on the normal life distribution and, when properly screened, are not expected during the normal life of a product at use condition. The random failure portion of the failure rate curve is the expected use condition time period during which those devices that are reliability hazards will fail predictably. The onset of wearout is defined by an increasing failure rate with time and is depicted by an upturn portion of the bathtub curve. It is clear that the useful life of a TMS 4164 is described by the random failure portion of the bathtub curve. The infant mortality occurs very early in life and the mechanisms within this time frame are frequently temperature-accelerated. The constant failure rate period is known as the useful life. A burn-in or run-in at the device or board/system level will aid in removing infant mortality. The cost of this operation must be weighed against the advantages of failure rate improvement and the reliability needs of the system. Several time-dependent models, including the Weibull and lognormal distribution, have been used to treat the time-varying failure rate.

Next to consider is a constant failure rate estimate after infant mortality removal with comments on preconditioning and its impact.

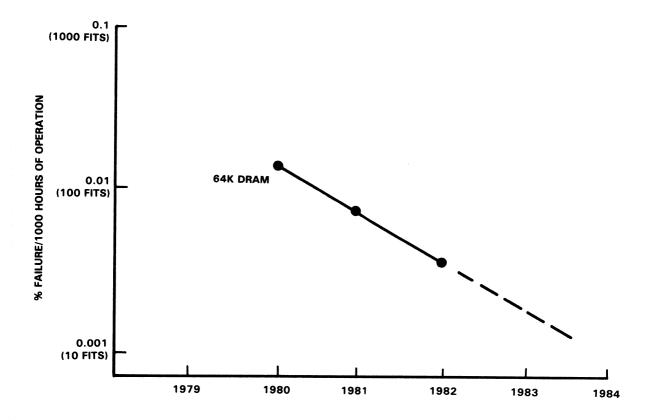

Extensive accelerated testing has been performed on the TMS 4164 process to define the failure rate distribution with associated failure mechanisms and to predict expected use condition reliability performance in time. Multi-temperature life tests are performed routinely on TMS 4164 series product line. The effect of temperature on failure rate is determined using the classical Arrhenius reaction rate model as it applies to semiconductor failure mechanisms.

The reaction rate constant is given as:

$$K = A_e^{-E/k_BT}$$

where kg is Boltzman's constant  $(8.63 \times 10^{-5} \text{eV/oK})$ ; A is a proportionality constant; E is the activation energy; and T is the absolute temperature. The life of a TMS 4164 is assumed to begin at the initiation (by some applied stress) of the reactions that occur on/in the chip and degrade device performance. Hence one may write:

$$\lambda \propto e^{-E/k_BT}$$

and plot the failure rate vs. 1/T to determine the activation energy for the failure mode of interest. From this information the acceleration factor (A.F.) between any two temperatures ( $T_1$  and  $T_2$ ) may be calculated from:

$$\frac{\lambda_2}{\lambda_1} = A.F. = e^{(E/K_B)x[(T_2-T_1)/T_2T_1]}$$

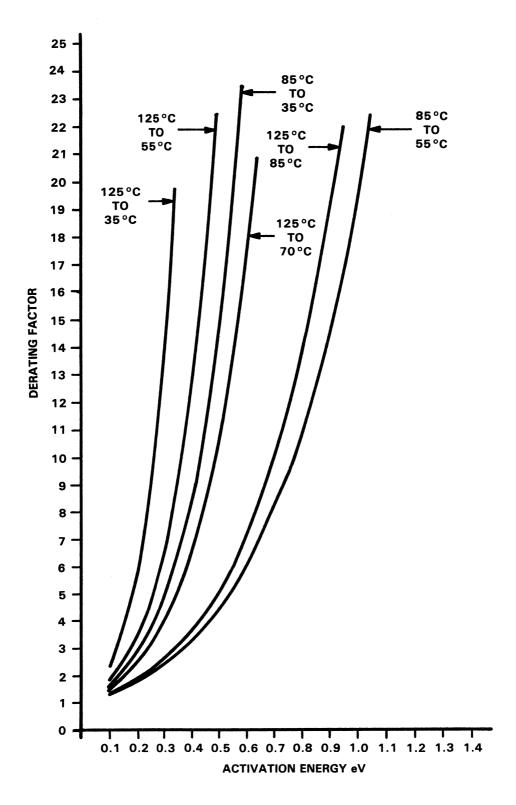

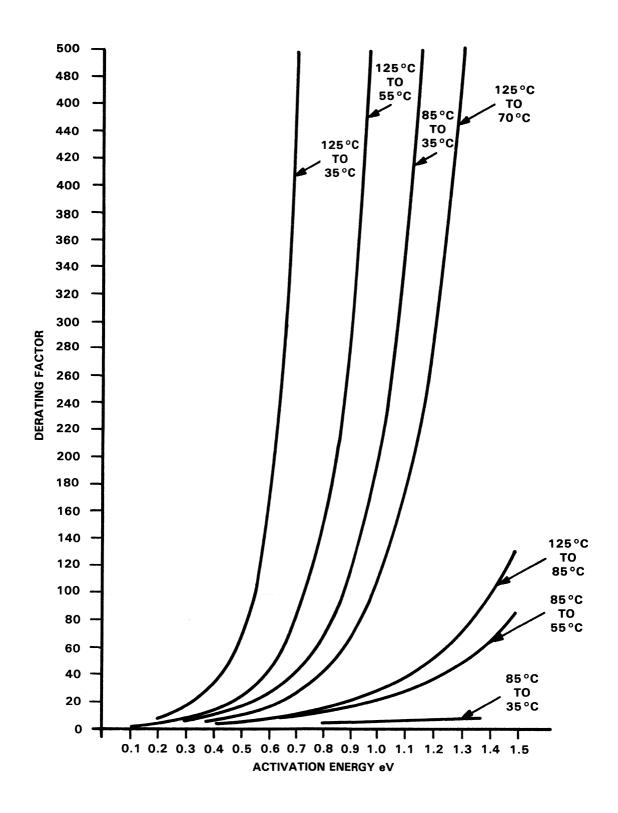

Included in Figures 14 and 15 are a series of curves generated from the acceleration factor expression that allow rapid approximation of acceleration factors for given activation energies. These curves can be used to estimate acceleration to be anticipated over various temperature ranges for the observed activation energy of any component. Of course, only after testing at various temperatures can the activation be determined. It can readily be seen that small changes in activation energy greatly affect the derating-to-use condition temperatures.

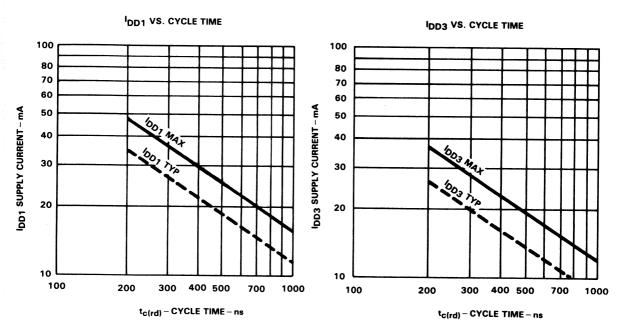

The overall TMS 4164 MOS process is characterized by a temperature activation energy of 0.5 eV for a composite of failure mechanisms, which is considered to be an extremely conservative figure. Device level testing in energized sockets at nominal voltages and at temperatures ranging from 35 °C to 125 °C are performed routinely to provide failure rate and activation information. Accelerated package testing is also conducted.

FIGURE 14 - DERATING FACTORS FOR VARIOUS ACTIVATION ENERGIES

FIGURE 15 - HIGHER DERATING FACTORS FOR ACTIVATION ENERGIES

#### **TEST FACILITIES**

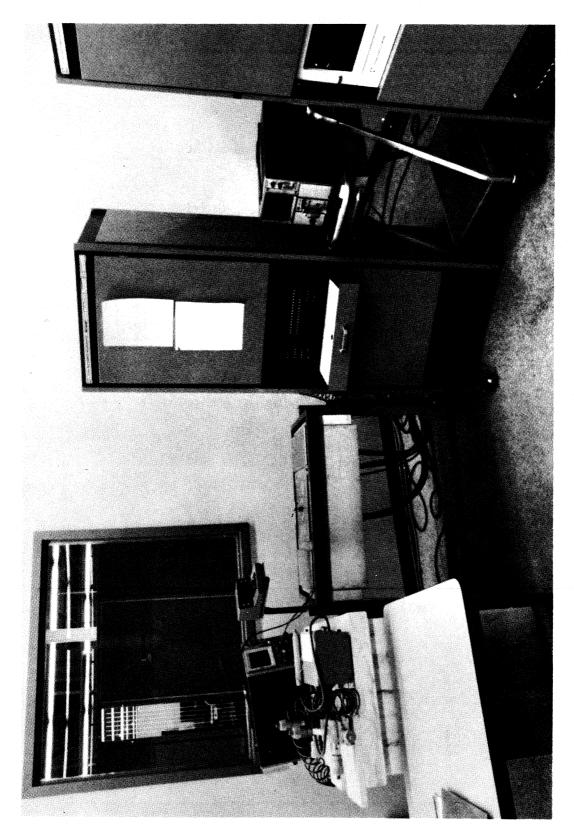

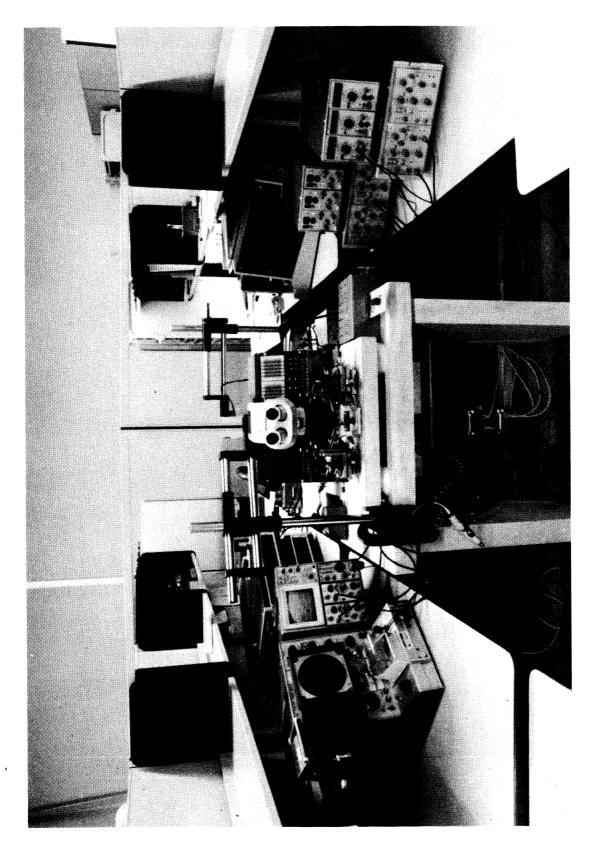

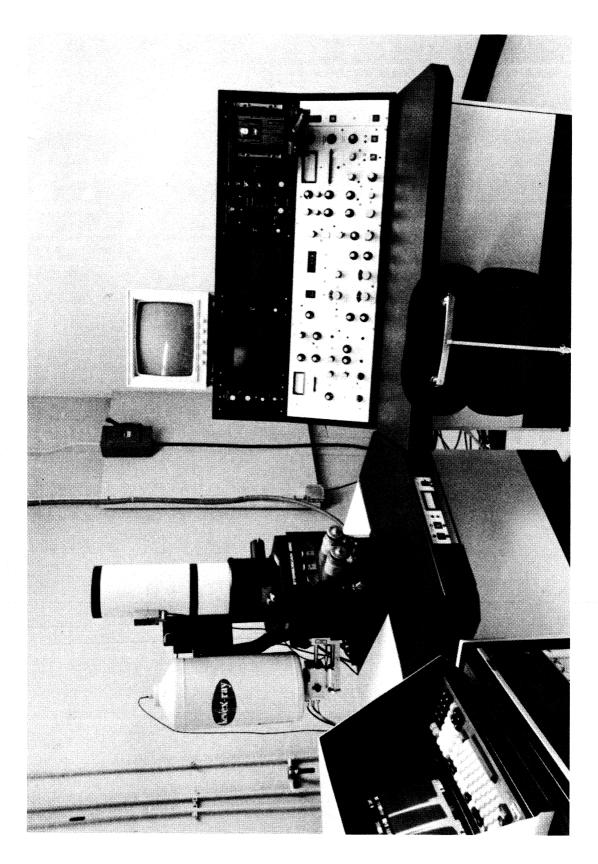

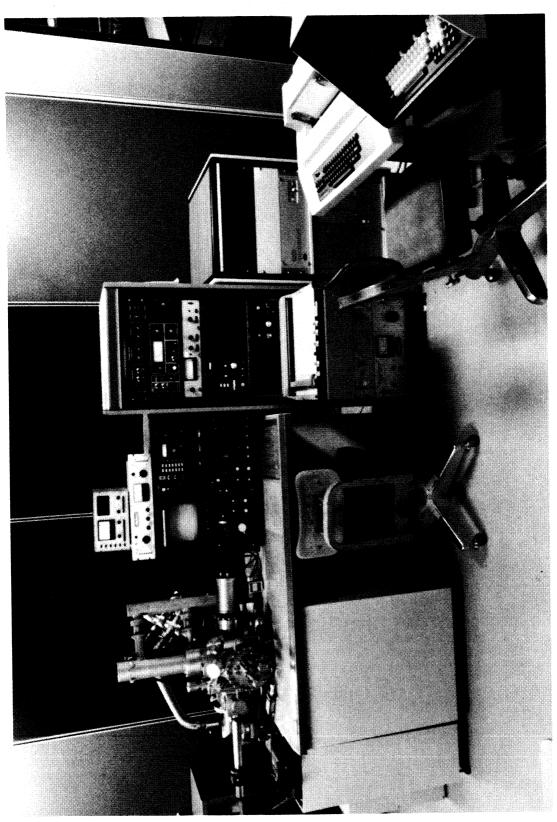

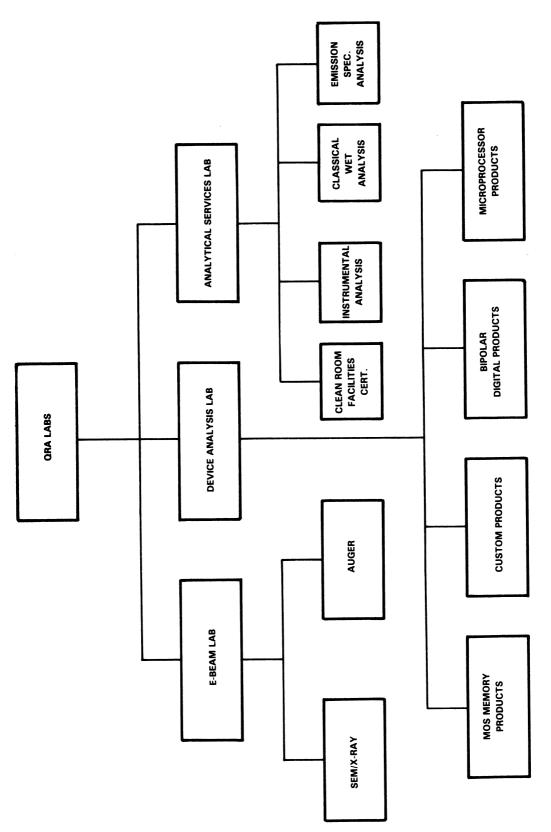

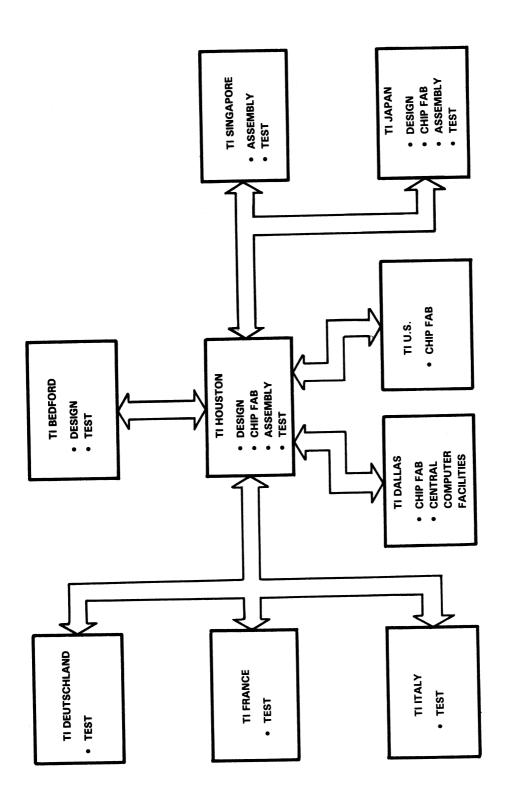

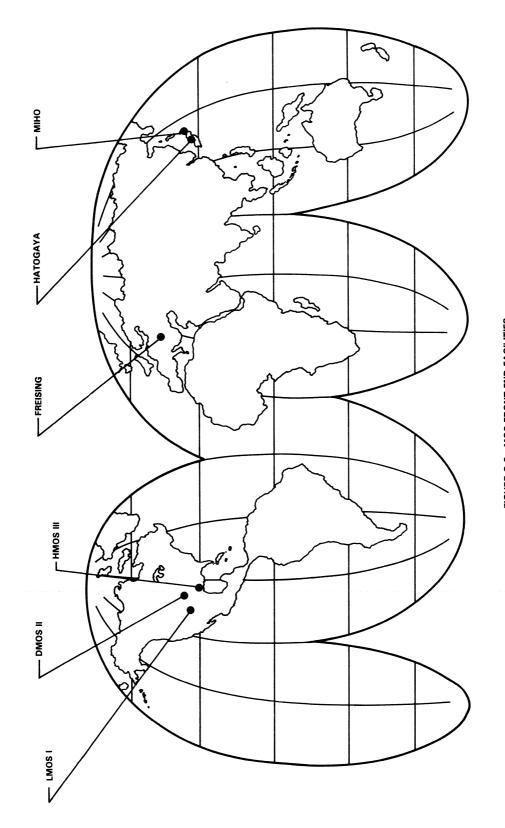

The people and equipment resources to implement the above procedure and flow represent considerable investment. Organization of the QRA laboratories in Houston, for instance, is shown in the chart in Appendix E. This organization primarily supports the analytical work on finished products and also services the Houston Diffusion Facilities. Similar facilities exist in Dallas, Lubbock, and Singapore to provide site support. The major equipment in the Houston laboratories is shown in the following illustrations. For initial failure analysis work, the Automatic Memory Tester, shown in Figure 16, coupled to a probe station exercises the questionable circuit. After analysis to determine failure symptoms, the Manual Probe Station (Figure 17) is used for internal probing to find the failed point. Further analysis must be done on a level-by-level basis, with emphasis on topology and chemical nature of the defect. Figure 18 shows a Scanning Electron Microscope coupled to an Energy Dispersion X-ray. Figure 19 is that of a Scanning Auger Microscope capable of examining the top 10-20 angstroms of an integrated circuit to indicate a chemical profile.

Peripheral support equipment within the laboratory includes complete chemical facilities for decapsulating plastic devices, delaminating chips to reveal defects, and performing various etching techniques including dry plasma etching. Also available are optical microscopy with photographic and mechanical screening capabilities. Since even simple current leakage problems may show up only under particular operating conditions, large scale integrated circuits, like the DRAM family, require advanced methods including scanning electron microscopy.

Several years of analysis of silicon-gate devices have contributed to a detailed understanding of the mechanisms that characterize the N-MOS process and DRAMS. The Device Analysis Laboratory at TI is the primary means for determining the physical cause of reliability hazards and proper corrective action by design, chip fabrication, or assembly processing staffs.

#### **ALPHA PARTICLE CASE**

#### THE PROBLEM

Since 1978, when alpha particles were found to be responsible for the generation of soft errors in memories, much work has been done to minimize the sensitivity of parts to these particles. The problem arises as geometries of new VLSI circuits reach dimensions that are affected by atomic events. The primary source of alpha particles causing soft errors is the decay of the trace amounts of uranium and thorium located in packaging materials for DRAMs.

Solutions to the soft error problem are being sought in these areas at TI:

- (1) Reduced package emissions

- (2) Shielding the device

- (3) Employing new processes and design techniques

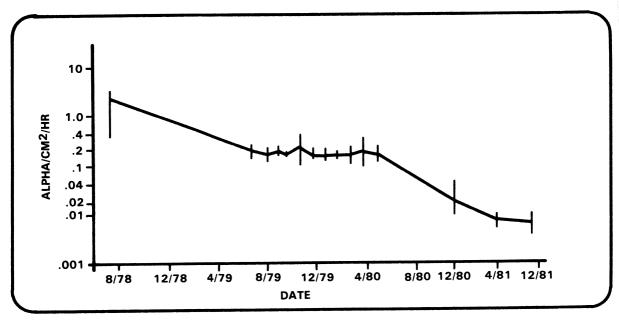

Figure 20 shows the relative reductions made in alpha emissions in ceramic packages since 1978. These reductions show a 200X improvement.

Adoption of the shielding approach has been announced by all manufacturers of 64K DRAMs. The type of shield varies but the end result is the same – adding a suitable thickness of material to the top of the chip to ensure alpha particles do not reach the active area of the device. This "overcoat" must be selected to have a low alpha emission rate, not cause any mechanical failures, not react chemically with the device, and be capable of withstanding processing.

#### THE SOLUTION

Twenty overcoat materials and processes were tested to find the best one for the 64K DRAM. Some materials broke wire bonds on temperature cycling; some would not take ceramic sealing temperature without decomposing; some became a source for ionic contamination; some caused moisture problems; some required elaborate schemes for application. The material finally chosen was subjected to rigorous quality and reliability tests. As a result, TI is now using single sided polymide tape on plastic devices and a potted polymide overcoat on ceramic units as shown in Figure 21.

Table 4 shows results of the initial alpha shield qualification tests. These tests were made with TMS 4164 as the test vehicle to insure that no compatibility problems were being overlooked.

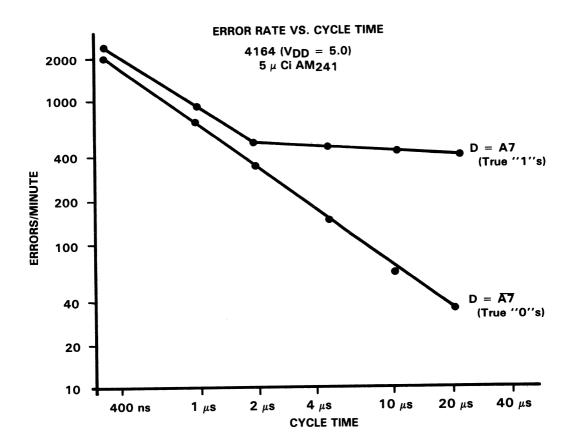

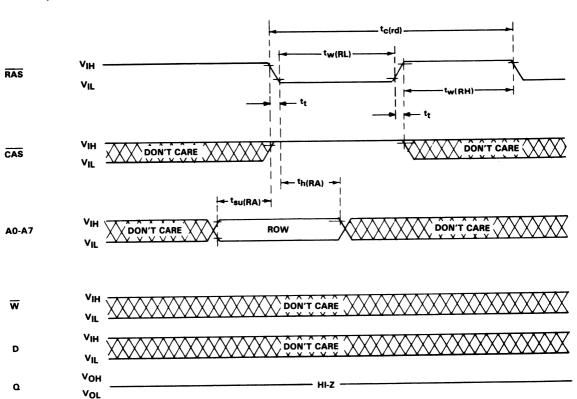

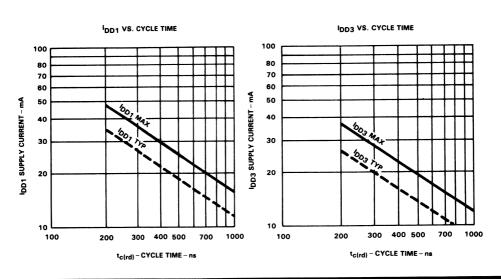

The sensitivity of the 64K DRAM to errors/min versus cycle time is shown in Figure 22. Using the alpha tester (see Appendix I), the curves were generated with decapsulated units and an alpha source located above the device. These curves illustrate a dependence on cycle time, indicating the alpha particles were causing errors due to hits on the bit lines. The flattening of the "true ones" curve shows the region where alpha hits on the cell became the predominant failure mode. Reduction in alpha sensitivity can thus be seen in Table 5 where errors in uncoated parts are compared to errors in overcoated parts.

GROUP **ENVIRONMENT** QUANTITY CONDITION RESULT 1 125°C Op Life 85 3000 Hour 2 Fail 2 T<sub>CV</sub> 65 °/150 °C 50 1000 Cy O Fail 3 **Bond Strength** 12 2011 Cy O Fail 50 Centrifuge/T<sub>Cv</sub> 1000 Cy 2001E 1 Fail 5 Max 5000 ppm Intercavity Moisture 6 Hi = 1691 ppmLo = 822 ppmAv = 1034 ppm

**TABLE 4 – ALPHA SHIELD QUALIFICATION TESTS**

sigma = 297 ppm

FIGURE 20 - ALPHA EMISSIONS REDUCTION

FIGURE 21 - TMS 4164 WITH PIQ OVERCOAT

FIGURE 22 - TMS 4164 ERROR RATE VERSUS CYCLE TIME

Below are the results of the accelerated alpha error tests performed on a random sample of TMS 4164 coated and uncoated parts. The tests were performed on an alpha test jig outlined in Appendix I.

#### **TABLE 5 - ERROR COMPARISON**

|                |                                    | (1) Source:   | 5 μCi Am <sub>241</sub>                                         |             |  |

|----------------|------------------------------------|---------------|-----------------------------------------------------------------|-------------|--|

|                | ERRORS PER MINU                    | TE OVERCOATED | ERRORS PER MINUTE UNCOATED                                      |             |  |

|                | (Test Duration                     | n = 20 min)   | (Test Durati                                                    | on = 5 min) |  |

|                | Cycle                              | Time          | Cycle                                                           | Time        |  |

|                | 500 ns                             | 5 μs          | 500 ns                                                          | 5 μs        |  |

| 1.             | 0                                  | 0             | 5661                                                            | 1615        |  |

| 2.             | 0                                  | 0             | 6268                                                            | 1695        |  |

| 3.             | 0                                  | 0             | 4799                                                            | 804         |  |

| 4.             | 0                                  | 0             | 6099                                                            | 1279        |  |

| 5.             | 0                                  | 0             | 5897                                                            | 1082        |  |

| A*             | 0                                  | 0             |                                                                 |             |  |

| в*             | 0                                  | 0             |                                                                 |             |  |

| c*             | 0                                  | 0             |                                                                 |             |  |

| D*             | 0                                  | 0             |                                                                 |             |  |

|                | ERRORS PER MINU<br>(Test Duration) | on = 5 min)   | ERRORS PER MINUTE UNCOATED  (Test Duration = 5 min)  Cycle Time |             |  |

|                | Cycle                              | Time          |                                                                 |             |  |

|                | 500 ns                             | 5 μs          | 500 ns                                                          | 5 μs        |  |

| 1.             | 3                                  | 2             | 6115                                                            | 1587        |  |

| 2.             | 5                                  | 4             | 5976                                                            | 1493        |  |

| 3.             | 5                                  | 3             | 5702                                                            | 1479        |  |

| 4.             | 5 4                                |               | 7075                                                            | 1836        |  |

| 5.             | 2                                  | 1             | 7428                                                            | 2208        |  |

|                |                                    | (3) Source:   | 100 μCi Cm <sub>244</sub>                                       |             |  |

|                | ERRORS PER MINU                    | TE OVERCOATED | ERRORS PER MINUTE UNCOATED                                      |             |  |

|                | (Test Duratio                      |               | (Test Duration = 5 min)                                         |             |  |

| $\perp \Gamma$ | Cycle                              | Time          |                                                                 | Time        |  |

|                | 500 ns                             |               | 500 ns                                                          |             |  |

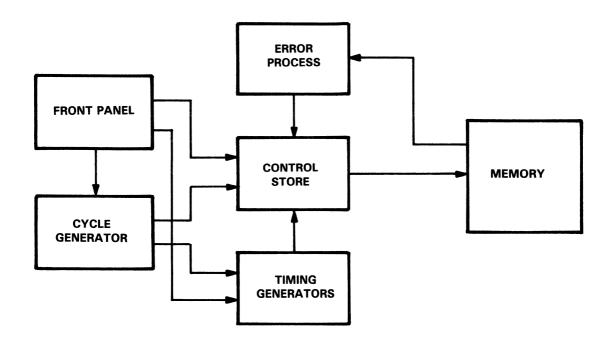

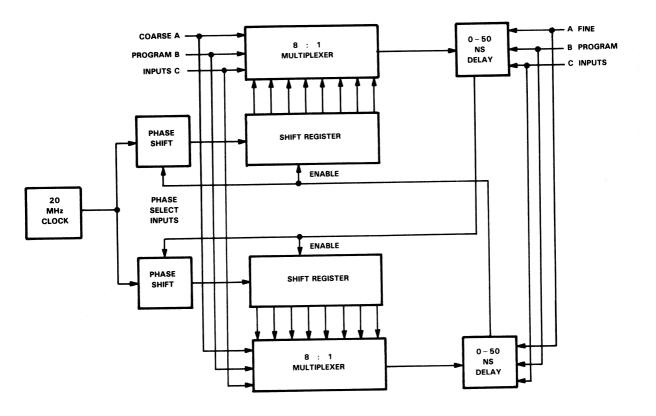

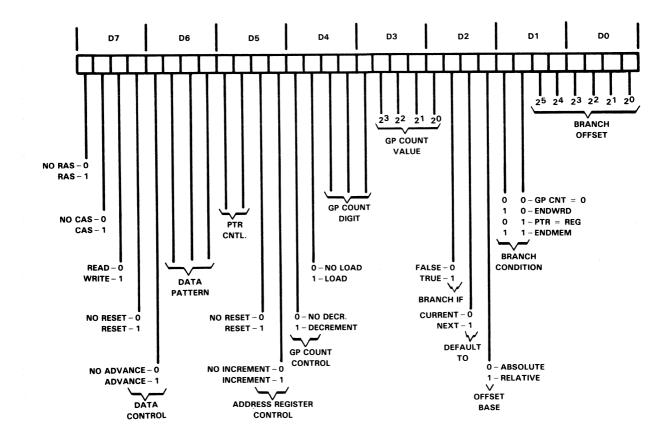

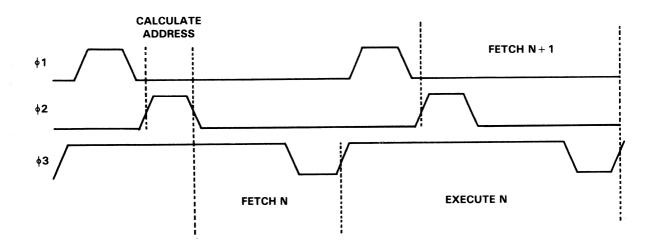

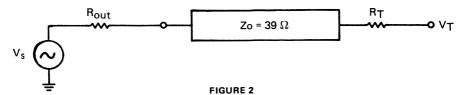

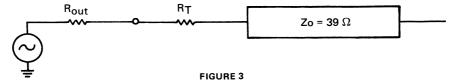

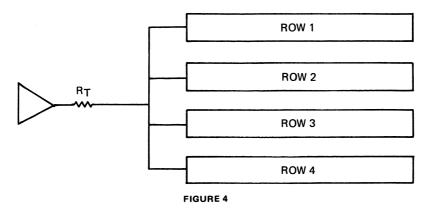

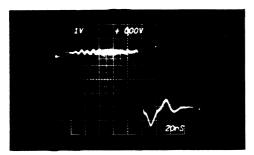

| E              | 0                                  |               | 464,000                                                         |             |  |